Friday, April 30, 2010

Learn Linting well, grab RTL Designer job @QCOM Bangalore

At CVC (www.cvcblr.com) we deliver high-end trainings to get recession affected engineers to get back to quality jobs. FOr instance if you are looking for a RTL design position you maybe interested in below job posting. Noite that LINT/CDC etc. is a MUST for such position nowadays. We at CVC deliver such trainings. Call us via 9620209226 for next LINT class from CVC. Also we deliver CDC trainings/project experience on need basis.

Job Function - Digital design and development (RTL)

- Ability to design and implement moderately defined tasks independently

- Unit level verification to meet various quality guidelines

- Lint, CDC, Synthesis, STA

Skills/Experience - 3 to 5 years of solid experience in digital front end design

- Expertise in Verilog

- Understanding of various bus protocols AHB, AXI will be added advantage

- Good documentation skills

- Previous experience with baseband MODEM design is a plus

- Ability to create unit level test plan

- Expertise in Spyglass Lint/CDC checks and waiver creation

- Expertise in Synopsys Design Compiler synthesis

- Expertise in Formal verification with Cadence LEC

- Expertise in Perl, TCL, Python languages is a big plus

- Understanding of RTL to GDS flow is desirable

- Working knowledge on timing closure is a plus

SystemVerilog engineers in demand in Bangalore

http://bit.ly/cJMmao

Requisition # G1879622

Job Title Sr Engineer - Verification

Post Date 4/29/2010

Division Qualcomm CDMA Technology

Job Area Engineering - Hardware

Location India - Bangalore

Job Function You will be contributing to the verification effort of a complex chip, core and/or blocks. You will contribute to defining chip level verification strategies, test plans and develop all necessary tools and scripts to enable system-level testing in an automated fashion. You will drive the block/core through coverage analysis and coverage optimization until coverage goals are met / exceeded. You will verify for interactions, connectivity, bus certification etc for robust verification. You will work with the Systems/Post Si/Driver development team to leverage software development on system level verification.

Experience with verifying SoC with embedded RISC/ARM/DSP processor verification, communications/ networking ASICs is a plus. RTL design experience is also a plus. Knowledge of wireless/wired communications and protocols or graphics/video multi-media a plus. As an individual contributor, you should take lot of initiative to take the verification automation to the next level. Candidate must have good organization and time and project management skills with excellent written and oral communications skills.

Skills/Experience Minimum 4-5+ years experience in ASIC/System verification

Expertise in verifying complex designs from system as well as block level, through design flow.

Domain experience in SoC Interconnects, communications modems, multi-media, peripherals, security desired.

Strong knowledge of HVLs (VERA/e), HDLs (Verilog/VHDL/SystemVerilog), C/C++.

Saturday, April 24, 2010

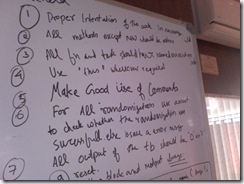

A glimpse of our DVAudit – what goes on @CVC’s TDG

Many have asked us the following:

- Is CVC a training company? I see: www.cvcblr.com/trainings

- Do you work on “live” projects?

- What is your TDG really doing?

and more. Usually these questions are more from students/RCGs (Recent College Graduates) than the experienced lot – as the experienced lot is well networked with CVC founders (www.linkedin.com/in/svenka3, www.linkedin.com/in/ajeetha) and can hence know about us well.

Our honest answer to such questions is “all of the above” :-) That’s YES, we ARE proud to be a training company www.cvcblr.com/trainings – simply b’cos we know why we are doing that. We work on “live” projects – we constantly upgrade to next generation technology, the most recent being the SystemVerilog VMM/OVM, Low power etc.

What makes us really different and keeps us constantly innovating is the thirst for “doing better”. This is the core of our PDG – Product Division Group (yet to be formally announced on our website), we look for ways to enhance the productivity. For instance when there is a customer deliverable for a Verification code, “Team CVC” spends quality time together to do thorough reviews, code walk through, custom lints etc. Here is our latest, weekend edition on un-moderated, live-from-the board glimpse of our DVAudit review done on a customer deliverable.

For the experienced lot reading this entry (BTW, thanks for getting so far :-)), this is such a common part of your tech-life. For those uninitiated, this is how industry works - “writing piece of code” is just A part – there is lot more to it in making it customer ready/production ready.

Now what’s innovative about the above “glimpse” – if you read it carefully you can observe that we are creating a thorough check-list of “executable” process for Design-Verification Audit. It is something CVC has been doing it for its corporate customers behind the scene for many years. Now it is slowly taking shape as part of our PDG – stay tuned for more..

Monday, April 19, 2010

Hiring 3-10 years exp SystemVerilog/VMM/OVM - immediate

Avinash Yadlapati Need OVM/VMM/System Verilog engineers with 3-10 years exp on an urgent basis. Please send resumes to avinash.amd@gmail.com asap

It ties well with our extended SystemVerilog classes from CVC, http://www.cvcblr.com wherein several mid-career engineers rehone their skills in Verification and get placed. A recent success is with Quartics @Pune.

Hello,

I joined Quartics last Friday. Have joined VLSI group here. The first thing I saw here is "A progmatic Approach to VMM Adoption" authored by you.

The training at CVC was very helpful. Got many interview calls after adding SV to my skill set.

Sunday, April 18, 2010

Appearing for a VLSI interview at CVC? Here are some tips..

Research yourself

It may sound kiddish, but researching yourself is an important part of any interview. Examining your interests, abilities, education, experience, values, and goals is the best way to prepare for the interview. Self-assessment is the best way to know your strengths and weaknesses. Be prepared to discuss concrete examples of things you have done in the past, whether on the job or in school.

Update your resume

Resume is the most important component while appearing for the interview. Your resume reflects about your skills, personality and traits. It is the replica of what you are and about what your have been till date.

If you are fresher, your project should be clearly elaborated and described in detail. There have been several instances where-in during our campus interviews from CVC we have seen resumes with no project detail at all. They stand for direct elimination as we at CVC primarily choose from that. In the project, clearly mention the implementation medium – say Verilog/VHDL/SystemVerilog, Layout (Virtuoso), Synthesis tool (Synplicity, Xilinx etc.).

Research the company

CVC looks for those who show an interest and an understanding of our business. It may assist you to become knowledgeable about the company . Researching the company meets two needs. First it allows you to evaluate whether or not you want to work here.You attitude should match with the company’s. Try to understand the expectations of the organization and then deliver accordingly.

The interview process is your chance to sell yourself. Knowing as much about the company as possible shows that you are interested in the position.

For CVC,

we highly recommend you read:

http://www.cvcblr.com

Visit the website

Try to analyse the website well and find out what it is trying to communicate. Half of the mystery will be solved through the website.

http://www.cvcblr.com

http://www.noveldv.com

Read The blog well

Most of your queries will be answered in the blog. The blog will give you a better picture about the organization.

For CVC, read:

http://www.cvcblr.com/blog

http://vlsi-india.blogspot.com

http://www.vmmcentral.org (Look for CVC contributed articles)

Read the job description carefully

Read about the position you are applying for and as to what CVC expects from you. Evaluate your qualifications, experience, and core competences, areas of strength .

Sleep well

Get a good night’s sleep the night before. This will help you to relax well while you are appearing for the interview and most important you should feel fresh and look fresh to start with a fresh job.

All the best

Webinar on Specman's next generation debug automation with SimVision

Here is some good news, CDN is conducting a free Webinar on Specman-SimVision combination on Apr 22nd. Currently it is scheduled for late evening @ 22.30 (around the IPL time frame :-) ). If there are enough interested attendees from India region, we can ask for a more convenient timing, just drop us an email via: info@cvcblr.com if interested.

Here is their Webinar info:

Specman/e Source Debug with SimVision Webinar

Are you using Cadence Incisive Specman Elite Testbench with Specview and interested in learning about SimVision?

If you’ve been using Specview with Specman/e and would like to learn all the key advantages of using the SimVision debug tool, this webinar is for you!

Date: April 22nd, 2010

Time: 10:00am PDT / 1:00pm EDT

Duration: 60 minutes

Sign Up Today! http://www.secure-register.net/cadence/q2_10_webinars_verification

The following topics will be covered in this webinar:

How digital design and verification engineers can reduce their learning curve by using SimVision as an integrated, unified debug environment for all standard HVL & HDL languages

e , SystemVerilog, Verilog, VHDL, SystemC, Verilog-AMS

Specifically, how a Specman/e user can easily migrate from the Specview debug environment to SimVision

How easy it is to visualize the extensions of objects in e code

How to customize the SimVision GUI for Specman users

Demo of SimVision debug and the key features will also be demonstrated

Learn multiple ways to set breakpoints/traces in:

Command line

Source Browser

Data Browser

Design Browser

….and many more user-friendly tips

Incisive Enterprise Simulator’s SimVision integrated debug environment supports signal-level and transaction-based flows across all IEEE-standard design, testbench, and assertion languages, in addition to concurrent visualization of the hardware, software, and analog domains. SimVision provides a unified simulation and debug environment that allows Enterprise Simulator to manage multiple simulation runs easily and to analyze both design and testbench behavior at any point in the verification process— regardless of the composition. Throughout the design and verification flow, SimVision provides hardware analysis checks, source browsing, transaction and waveform viewing, and complete code/ transaction/assertion coverage analysis. Application programming interfaces based on industry standards are available at all levels to enable user-defined checks and analysis.

Who should attend:

Specman/e users who want to learn how to use Specman/e with SimVision

Incisive Enterprise Simulator (IES) users who have or are planning to switch to 9.2 release

Customers who want to learn more about the SimVision ease of use

Sign Up Today! http://www.secure-register.net/cadence/q2_10_webinars_verification